## TG7200C

# 原理图说明与 PCB LAYOUT 指南

V1.0

### 目录

| 1. 参考原理图         | 3  |

|------------------|----|

| 1.1 总体原理图参考      | 3  |

| 1.2 RF 输出线路      | 3  |

| 1.3 部分电源及其滤波电容说明 | 4  |

| 1.4 无源晶体         | 6  |

| 2. Layout 指南     | 7  |

| 2.1 天线匹配电路       | 7  |

| 2.2 芯片射频输出匹配     | 7  |

| 2.3 电源相关         | 7  |

| 2.4 无源晶体         | 9  |

| 2.5 通孔和覆铜接地      | 9  |

| 2.6 必要接口的引出      | 10 |

为了确保 TG7200C 具有良好的射频性能,避免不必要的硬件改版提高产品开发效率,在使用 TG7200C 进行 PCB LAYOUT 时,务必参考下面的建议。

#### 1. 参考原理图

#### 1.1 总体原理图参考

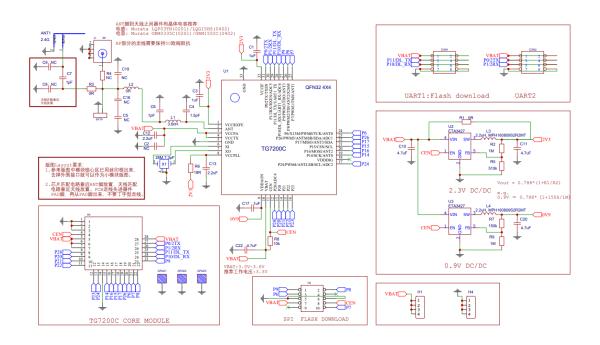

TG7200C 的整体参考原理图,如图 1:

图 1

右上角为两组引出的 UART 接口,其中 UART1 作为 FLAHS 下载和一般调试用;

其下为可备选的外部电源管理芯片模块,如若有额外的低电流工作要求可以采用(R1需要NC)。DC-DC芯片选型为钰泰 ETA3427。一般应用情况下,该框图内除 R1 = 0R,其他器件均不需焊接;

下部中间为引出的 SPI 接口;

其左 TG7200C CORE MODULE 将芯片主要 GPIO 和电源引出;

未框选的是芯片主要核心布局,主要为各个电源的滤波电容和 RF 输出线路;

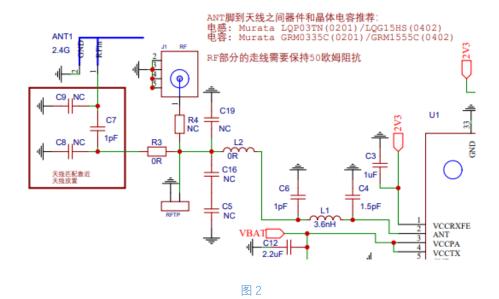

#### 1.2 RF 输出线路

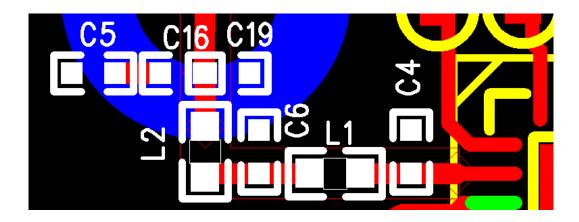

C4 L1 C6 为主要的匹配调节网络。C19 C16 C5 为 FCC 认证预留的滤波电路。R3 R4 用于调整切换 RF 输出路径: SMA 或板载天线,默认应当 R3 = 0R,R4 = NC,使用板载天线。C8 C7 C9 为天线匹配电路。

#### 1.3 部分电源及其滤波电容说明

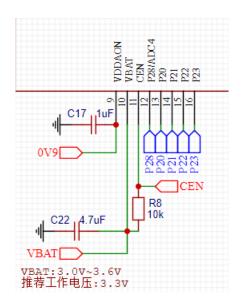

首先说明芯片的总供电 VBAT, 推荐工作电压为 3.3V, 如图 3 所示。C22 为芯片 VBAT 用的滤波电容, 综合成本和 PCB 空间考虑推荐选用合适耐压的 4.7uF 0603 封装的陶瓷电容。

图 3

图 3 中 CEN 引脚为 CHIP ENABLE 芯片使能引脚,推荐使用 VBAT 网络经 10k 电阻上拉使能。

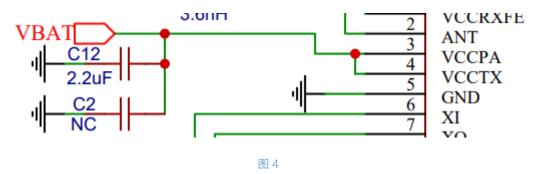

图 4 所示为芯片 RF 功能供电,VCCPA 和 VCCTX,需要使用 VBAT 网络经 2.2uF 滤波提供,一般可仅用 2.2uF,C2 为冗余预留。

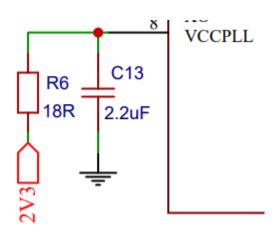

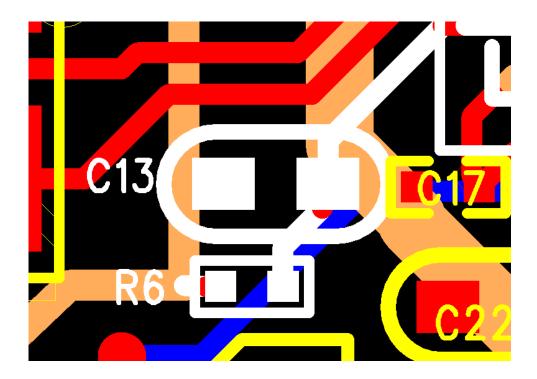

图 5 所示为 VCCPLL 锁相环供电。2V3 的网络标签原本是外部电源芯片的降压输出,若如 开头所言选用 R1 = 0R,未使用外部 BUCK 时,2V3 与 VBAT 是用 0R 连接所连通的。该网络经过 LC 滤波后为 VCCPLL 供电,R6 =18R 和 C13 = 2.2uF 需要严格贴近芯片保留。

图 5

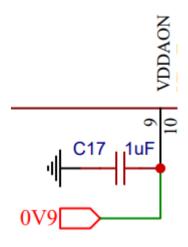

图 6 所示 VDDAON 为芯片内电源域。0V9 的网络标签原本也是外部电源芯片的降压输出,不使用外部 BUCK 时,芯片内部供电,仅需保留 C17=1uF.

图 6

其余的 VCCIF VCCRXFE 参考原理图即可。

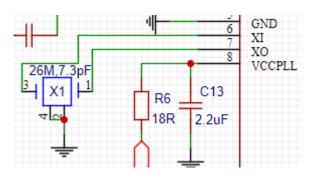

#### 1.4 无源晶体

无源晶体推荐选用 26M, 7.3pF。参考板上的元件型号为晶威特 CF4026M000739FA40000.

图 7

#### 2. LAYOUT 指南

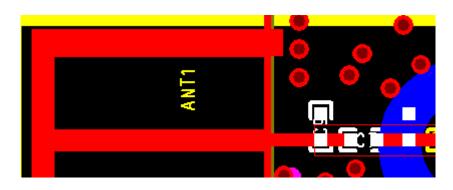

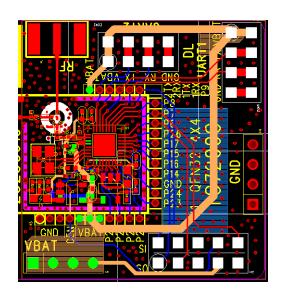

#### 2.1 天线匹配电路

如图 8, C7 C8 C9 为天线 pi 型匹配预留位置,靠近天线放置,三个匹配元件靠近且最短走线。 控制线宽和铺铜距离,需要保持 50Ω.

图 8

#### 2.2 芯片射频输出匹配

C4 L1 C6 为芯片 RF 匹配元件,靠近芯片 ANT 引脚放置,三颗匹配元件靠近且最短走线,L2 C19 或者 L2 C16 C5 为 L 型低通滤波器,主要为了滤谐波,C16 和 C19 二选一共用一个PAD。控制线宽和铺铜距离,需要保持 50Ω.

图 9

#### 2.3 电源相关

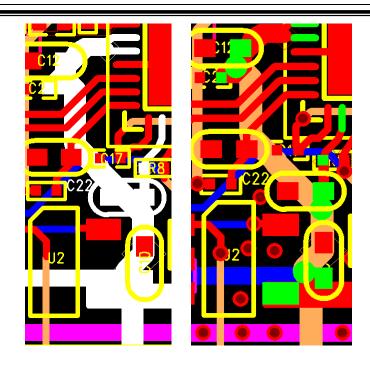

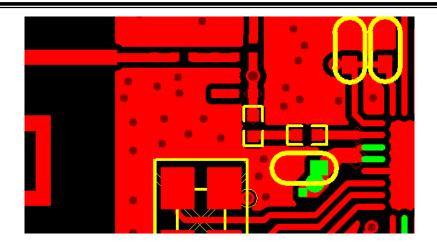

VBAT 电源走线需尽可能宽,线宽尽量保持 0.5mm 以上,推荐 1mm 宽,尤其是经过 C2, C12 到 VCCPAD VCCTX 要保持足够线宽。参考 PCB 为四层板,第二层为完整地平面,第三层为电源相关走线,如图 10 和图 11。如果采用两层板,电源走线需要避开 RF 输出线路。

图 10 和图 11

VCCPLL 的供电线路上,R6 和 C13 需要尽量靠近芯片引脚放置,如图 12.

图 12

其余电源相关,VCCRXFE VCCIF VDDAON 的滤波电容也都需要贴近芯片引脚放置。

#### 2.4 无源晶体

X1 为 26MHz 晶体, 晶体 XI XO 走线下方不要有电源线和其它走线, 接地 PIN 通孔连接到 其他层的地, 需要限制 TOP 层的覆铜区域使得晶体的地网络与 Top 层的地隔离, 如图 13.

图 13

#### 2.5 通孔和覆铜接地

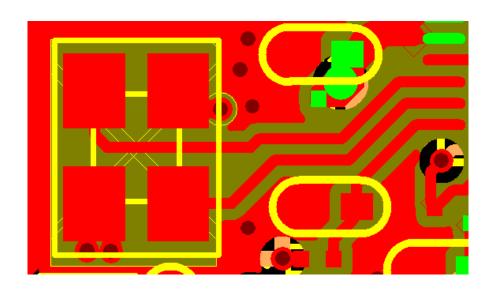

所有的接地管脚附近都必须打过孔连接到地上,芯片的基底一般需要打 16-25 个地过孔,越多越好。每个元件的 GND PAD 附近需要放 2-3 个过孔,芯片、射频匹配和晶体的下一层要保持完整的地,除射频测试点外不要有其他走线,如图 14.

图 14

RF 路径需要良好的地网络覆铜,两侧尽可能多打过孔,如图 15.

图 15

#### 2.6 必要接口的引出

RF、UART1、UART2、SPI 测试点必须预留,如图 16,否则无法正常调试和产线量产测试。

图 16